FPGAs’ Benefits to SDRs

Introduction

Radio communication has come a long way since the days of analog transmissions. In the modern industry, digital-based radio platforms called software-defined radios (SDRs) can outperform conventional hardware-based systems by implementing most RF functions on the software side, obtaining unparalleled flexibility and efficiency. The secret of this success lies in the digital backend based on a powerful (and highly versatile) integrated unit: the field-programmable gate array (FPGA). These high-performance semiconductor devices are based on a reconfigurable matrix of logic blocks that can be precisely programmed to perform a wide range of digital functions, including digital signal processing (DSP) algorithms. When integrated into SDRs, FPGAs provide several benefits that can significantly improve performance and enable novel and condition-specific applications. Because the actual internal structure of the FPGA can be reprogrammed after manufacturing, these devices provide much lower latency than CPUs and more flexibility than ASICs. Therefore, these ICs are ideal for applications that require high-speed processing, low latency, and real-time performance. In the context of SDRs, FPGAs can improve channelization capabilities, perform advanced modulation/demodulation schemes, and implement high-speed backhaul interfaces.

In this article, we will discuss the different features of FPGAs and how these characteristics impact the performance of commercial off-the-shelf (COTS) SDRs. We will explore how primary FPGA resources, including logic elements (LEs) and Adaptive Logic Modules (ALMs), can limit or expand SDRs’ capabilities in channelization and signal processing, such as filtering, decimation, interpolation, and mixing. Furthermore, we will relate the central SDR figures of merit, including bandwidth, number of channels, and backhaul interfaces with FPGA requirements, to better guide FPGA selection when designing a transceiver. Finally, we discuss how FPGA-based SDRs can impact critical RF applications like radar, spectrum monitoring, and electronic warfare.

What is SDR?

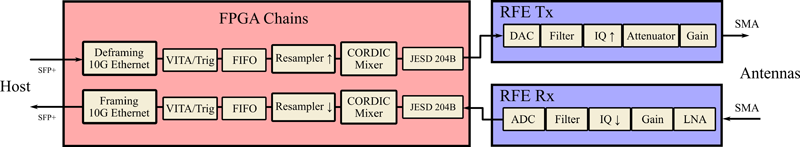

To understand the impact of FPGAs on SDR performance, we should first review these transceivers’ basic concepts and working principles. SDRs are simply radio units capable of performing most of the RF functions on the software side, in contrast with conventional radio systems that rely entirely on hardware. Because of this fundamental characteristic, SDRs can be completely changed, tuned, and reprogrammed on-the-fly without any hardware modification by simply uploading new code. The architecture of SDRs can vary with brand and model, but the general architecture can typically be reduced to two main components: the radio front end (RFE) and the digital backend. The RFE contains all the necessary hardware to enable receive (Rx) and transmit (Tx) radio functions, allowing the SDR to operate over a wide tuning range and high instantaneous bandwidth. In fact, the highest-bandwidth SDRs in the market can provide tuning ranges from DC to 18 GHz, upgradable to 40 GHz, with instantaneous bandwidth ups to 3 GHz per channel. Furthermore, multiple-input multiple-output (MIMO) SDRs provide multiple RFE channels that can be operated in parallel thanks to independent ADC/DAC chains, enabling one device to perform many functions simultaneously. The precision of the RFE is crucial for overall performance, so selecting SDRs with high-dynamic range and low noise-figure is paramount for success in critical applications, such as spectrum monitoring and radar. On the other hand, the digital backend is where most of the RF functions are performed in an SDR, including modulation/demodulation, up/down-converting, data packaging, decimation, and interpolation. In this stage, high-end SDRs typically implement powerful FPGAs with onboard DSP capabilities so that all the functions programmed in the FPGA can be completely reprogrammed at any point of the life of service, providing a whole new level of flexibility and adaptability that is fundamental to address current needs of the RF industry. Therefore, FPGAs play a significant role in SDR performance. Figure 1 shows a block diagram of a basic SDR architecture that highlights the role of FPGA in SDR, including CORDIC mixers, JESD 204B interfaces, framing/deframing of Ethernet data, and implementation of VITA 49 transport standard.

Now let us discuss a little bit about FPGAs. Field-programmable gate arrays, as the name suggests, are semiconductor units where the connections between internal gates can be wholly programmed at will so that the hardware itself is modified instead of just code instructions. Therefore, FPGAs combine the low-latency application-specific performance of ASICs with the programmability and flexibility of microprocessors. The basic architecture of an FPGA is composed of a matrix of configurable logic blocks (CLBs) that can be programmed into a variety of logic gates and flip-flops, with densities ranging from 500 kLE to 10.2 MLE. Thus, FPGAs are capable of heavy parallel computing, which further enables these devices to work with very high data throughput – crucial for MIMO SDRs. These devices also provide data interfaces for communicating with peripherals, including the RFE DACs, ADCs, and the host backhaul, typically performed by Ethernet controllers. To make this possible, FPGAs require both the physical resources on the chip (number of transceivers and speed grades) and the proper IP cores to drive the interface, like JESD and 10/40/100G Ethernet. FPGAs can also provide onboard embedded processors implemented in system management and configuration, complex algorithms, and some DSP functions.

There are several reasons why using FPGAs in the digital backend of SDR systems is extremely beneficial for both the device and the application. Firstly, these devices provide very low latency due to their parallel computing architecture, allowing for latency control at the clock cycle level, which is critical in applications such as 5G networks and electronic warfare. Essential DSP functions, such as digital upconverting/digital downconverting (DDC/DUC), filtering, mixing, interpolation, and decimation can be implemented much faster than in conventional microprocessor units. Additionally, FPGAs can handle sample buffers, framing/deframing of data, and packetization of IQ data into the network protocol stack, typically using the VITA49 standard to exchange IQ data between the host and SDR. Furthermore, FPGAs are often used for Serializer/DeSerializer (SerDes), Serial-In Parallel-Out (SIPO), and other helpful shift registers. FPGAs can also efficiently perform channelization, an extremely useful feature in SDRs where a single input signal can be split into multiple DSP channels for independent data processing. Finally, the main reason why FPGAs are used instead of ASICs is the ability to be reprogrammed entirely on the fly, allowing general-purpose COTS SDRs to be programmed to work with virtually any function.

When selecting an FPGA for an SDR, it’s essential to define the performance goals and the critical requirements of the system, such as the number of radio chains and the target bandwidth per chain. Different FPGAs have different numbers and speeds of transceivers, which will limit the capabilities of radio chains, especially in MIMO operations. For instance, if you don’t have enough peripheral transceivers, you cannot support as many independent ADCs and DACs at your RFE board, which will consequently limit the number of radio chains. Similarly, the overall bandwidth will be significantly limited if the transceiver speeds don’t support the ADC/DACs sampling rates. FPGAs for high-end SDRs also need multiple high-speed transceivers to support high data throughout the backhaul, such as 40-100 Gbps Ethernet links. Different FPGA families provide other digital capabilities, so selecting the proper model/family is fundamental to optimizing SDR performance.

Critical applications benefiting from FPGAs in SDRs

Radars implementing beamforming/beam-steering technologies benefit greatly from FPGAs, primarily due to the parallel computing and channelization capabilities. In large-scale beamforming systems with hundreds of antennas, several FGPAs can handle a portion of signals (up to 16 antennas per FPGA). For each antenna signal, the FPGA can divide the bandwidth into multiple portions for independent parallel processing, which are then modified by a phase slope, that is different for each antenna in the array. Each signal in a beamforming array must be properly aligned to compensate for differences in cable length. Finally, the partial channelized beams formed by each FPGA are summed together in one FPGA for processing. Thus, modern beamforming radars rely greatly on FPGA systems for proper operation.

Another important application that can benefit from FPGAs is wide-band spectrum monitoring and recording. To capture and record wide-band signals, multi-giga sample/second sampling is required, which requires extremely fast ways of communicating between the ADC from the RFE and the FPGA backend. In this endeavor, the JESD204B protocol is the interface of choice for data exchange, especially when implementing ADCs in the GSPS range. Wide-band ADCs provide high sampling rates, which are crucial to capture large portions of the spectrum per channel. FPGA selection plays a critical role in ensuring optimal performance in wide-band spectrum monitoring and recording applications, as it determines the number and speed of transceivers available to interface with the ADCs, the amount of programmable logic available for signal processing, and the memory bandwidth available for storing and retrieving the captured data. The bandwidth can be split into several portions independently monitored by different MIMO channels, and simultaneously processed to provide high data throughput. The ability to work with multiple signal chains in a parallel fashion makes FPGAs the best choice for spectrum monitoring.

In electronic warfare applications, FPGA-based SDRs are crucial for various critical functions, including signal intercepting, jamming, spoofing, deciphering, and signal intelligence (SIGINT). These systems require high-speed processing and real-time decision-making capabilities, which are powered by the SDR’s extremely low latency and heavy parallel computation capabilities. The parallel architecture of FPGAs allows for fast execution and response times, which is crucial in EW operations where quick reactions are critical. FPGAs can also be programmed to implement complex algorithms, such as state-of-the-art communication protocols, encryption and security schemes, and artificial intelligence programs/machine learning architectures. However, it is important to consider the trade-off between latency and FPGA resources when designing SDRs for EW applications: high-performance FPGAs can reduce overall latency. However, increasing the implementation complexity can also require more resources and improve the overall cost of the system.

Benefits of Using SDRs with FPGAs

One of the significant advantages of using SDRs with FPGAs is the high level of flexibility and reconfigurability that they provide. With FPGAs, it becomes easier to modify and upgrade the functionality of the SDR without having to replace the entire hardware and with minimum human intervention. This enables the transceiver to quickly adapt to new requirements and integrate with other systems seamlessly. Moreover, FPGA-based SDRs can be designed to be platform-agnostic, which means they can work with different types of hardware and software platforms, such as GNU Radio and other open-source systems. This makes integrating the SDR into large existing architectures easier and enables the communication between different systems. Additionally, FPGA-based SDRs are highly scalable and can be easily adapted to meet changing requirements. As a result, COTS transceivers can be used in a wide range of applications, from commercial wireless systems to military communication and radar systems.

By using readily available HDL IP cores for FPGAs, SDRs can benefit from many functionalities and capabilities without requiring extensive development time. The availability of open-source HDL libraries shared and developed by a community of amateurs and professionals allows for the efficient scaling of FPGA designs. This can significantly reduce costs and development time for RF projects. In the past, IP cores were often proprietary and required costly licensing, making them inaccessible to smaller research projects or startups. However, the availability of open-source FPGA cores has democratized access to robust FPGA designs for various applications, from IIR/FIR filters and oscillators to IQ pair phase and gain correction codes. Overall, using HDL IP cores for FPGAs can significantly enhance SDRs’ capabilities and versatility while reducing development costs and time. Naturally, if there is no IP core available for your SDR application and you’re looking to develop one from the ground up, SDR manufacturers have a lot of available resources for custom development. If you have an FPGA engineer, this becomes a feasible option for developing and implementing custom algorithms.

Conclusion

Software Defined Radios (SDRs) have emerged as a powerful tool for signal processing and communication systems in today’s constantly evolving communication technologies. Field Programmable Gate Arrays (FPGAs) have proven to be a popular digital backend for SDRs, providing a high degree of flexibility and scalability while improving the transceiver’s overall performance. FPGA-based SDRs are helpful for several RF applications, including wide-band spectrum monitoring and recording, electronic warfare, and beamforming technologies. The advantages of using FPGAs include easier integration with existing systems, readily available HDL IP cores for various functions, and the ability to develop custom algorithms for specific SDR applications. Overall, using FPGAs in SDRs has significantly improved their performance, flexibility, and functionality, making them indispensable for modern communication systems.

About Per Vices

Per Vices has extensive experience designing, developing, building, and integrating SDRs for various applications. Contact solutions@pervices.com today to see how we can help you with your