SOSA-Aligned WILDSTAR 3XR0 Board Integrates Two Gen 3 RFSoCs and Enables 18+GHz Digitization

Annapolis Micro Systems has developed the first SOSA™-aligned 100Gb Ethernet FPGA board that combines the processing and A/D & D/A converting power of two Gen 3 Xilinx UltraScale+™ RFSoC FPGAs, with the ability to incorporate 18+GHz digitization.

The WILDSTAR™ 3XR0 3U OpenVPX FPGA Processor incorporates an innovative full-length coax-connected Analog Interface Mezzanine Site. This site can be populated with a direct RF digitization mezzanine, or a 3rd party analog superheterodyne tuner to allow for the digitization of 18+GHz signals.

An integrated tuner delivers much lower SWaP-C than a separate standalone tuner while maintaining the ability to upgrade the tuner and digitizer/processor separately.

“We don’t know of anyone else who is combining this much tuning, digitizing, and processing capability in a single 1” VITA 48.1 slot,” said Noah Donaldson, Annapolis Micro Systems Chief Technology Officer.

In addition to two Gen 3 RFSoC FPGAs (XCZU43DR & some other P/Ns on request), an on-board Xilinx MPSoC (XCZU5EV) provides high performing yet low power self-hosting capability thanks to the power-efficient ARM cores.

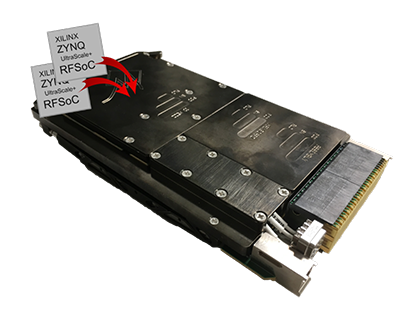

The rugged 3XR0 supports wide temperature ranges via air, conduction (photo above), or air-flow-through cooling. Min/max operating temperatures are -55˚C/85˚C; min/max storage temperatures are -65˚C/105˚C.

For maximum flexibility, the 3XR0 supports SOSA and/or VITA 65 backplane slot profiles architectures. It also offers optional VITA 67 backplane RF connectivity.