The evolution never ends: PICMG announces new MicroTCA specifications

PICMG announces that the MicroTCA Working Group is working on the next generation of the MTCA architecture specifications initially launched in 2006. Efforts target improvements for time-sensitive and high bandwidth applications such as in high-energy physics. Current work includes accommodations for the next generation of CPUs and FPGAs that will natively support PCIe gen 5. Future applications in the industry require this higher bandwidth i.e. for image processing, signal detection, and data acquisition. As current CPU speeds are limited by 80 W per slot power limit the support of more power for faster CPUs is on the task list as well. Future applications will also require other kinds of high- and low-speed fabrics paired with more flexibility in system design. The science market segment for high frame rate Megapixel detectors of the actual photon experiments requires even higher throughput. Thus, all these demands are scheduled to become part of the new releases of these successful specifications. With all these improvements MicroTCA continues to be a proactive specification with significant updates to support high-bandwidth backplane interconnects. The latest update of the specs happened as recently as 2020.

“I am more than happy that the MicroTCA Working Group is so pro-actively addressing the recent demands. The new spec will find its way into many different vertical markets due to the flexibility of MicroTCA!”, says Heiko Koerte, VP and Director Sales & Marketing of N.A.T., “Applications in industrial automation, medical, telecommunication, and networking, aerospace, and transportation will not only benefit from these new features but also from how easily MicroTCA can be adapted to the exact needs. More than 16.500 MCHs just from N.A.T and many more I/O and compute cards delivered to the field speak for themselves. The wide spread of MicroTCA makes it both a technically and commercially attractive solution!”.

About MicroTCA

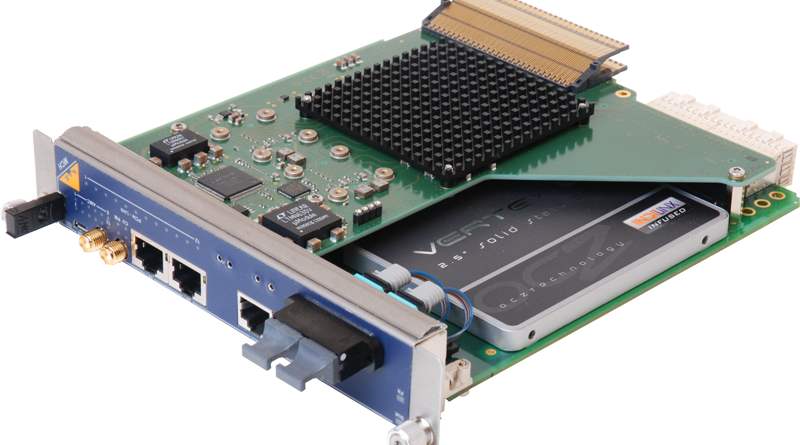

MicroTCA® is a modular, open standard for building high-performance, backplane-based switched fabric computer systems in a small form factor.

MicroTCA has become the de facto standard for precision timing and synchronization equipment at world-renowned particle accelerators CERN, DESY, ESS, XFEL, KEK, SLAC, and others. Its architecture and features are also consistent with the Modular Open Systems Approach (MOSA) being adopted as part of the U.S. Department of Defense (DoD) electronic media acquisition policy.

Originally designed for edge telecom and networking use cases, the core MTCA.0 base specification defines the mechanical and electrical characteristics of a MicroTCA backplane, card cage, power subsystem, cooling, and system management. Since being ratified in 2011, the MTCA Base specification has been revised to support 10GBASE-KR and 40GBASE-KR4 Ethernet fabrics and spawned four additional sub-specifications adapted for data acquisition, control, and telemetry in markets such as high-energy physics, avionics, defense, mobile infrastructure, and others.